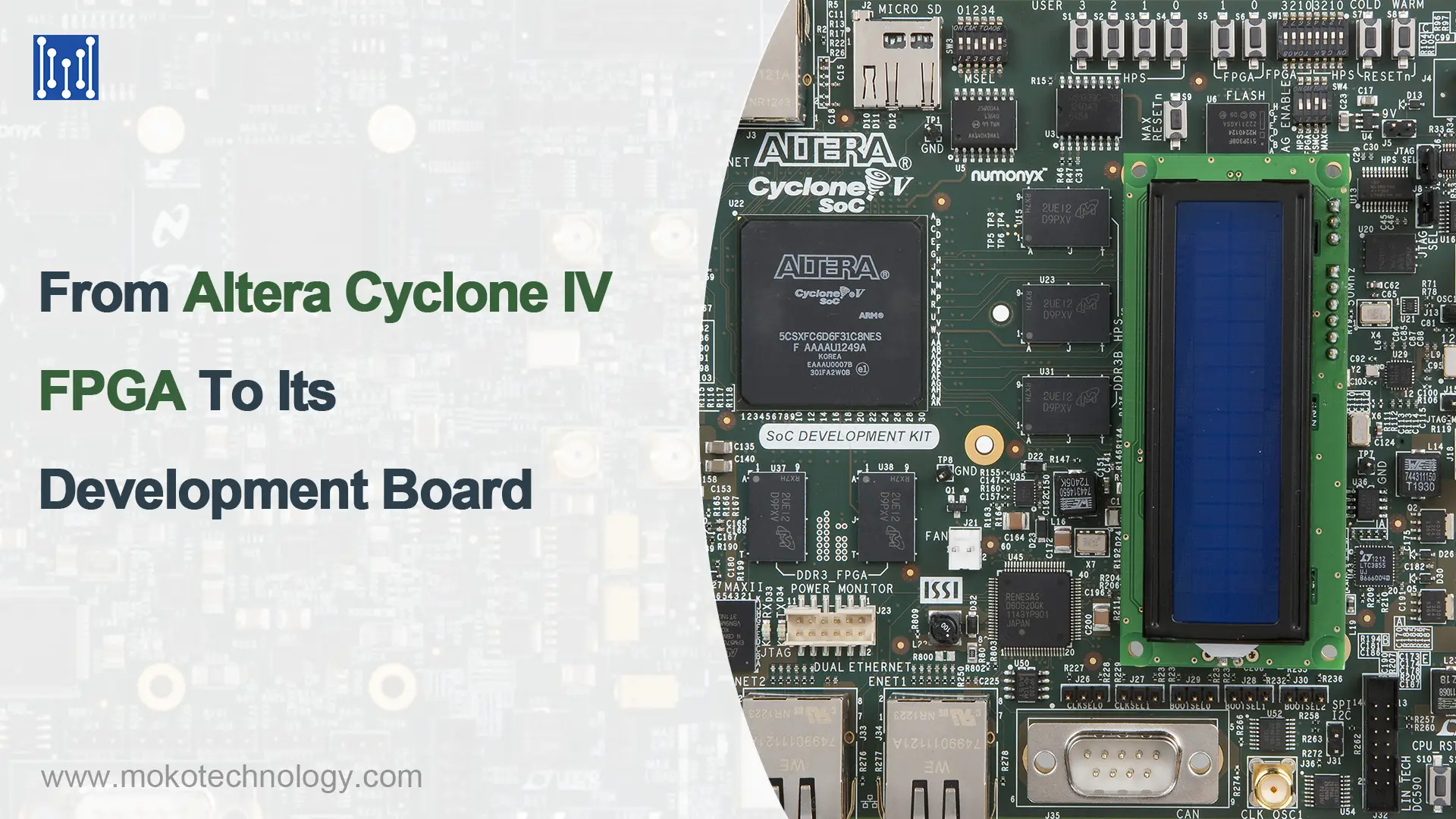

Nowoczesna dziedzina produkcji elektroniki jest świadkiem popularności płytki rozwojowej Altera Cyclone IV FPGA. Ten tekst poinformuje Cię o czymś ważnym, od Altera Cyclone IV FPGA po płytkę rozwojową, łącznie ze specyfikacją chipa, funkcje chipa, podejście do wejścia na pokład z tym chipem, pytanie dotyczące tworzenia płyty z Altera Cyclone IV FPGA i niektórymi wysoce zalecanymi Altera Cyclone IV FPGA PCB. OK , teraz zagłębimy się w nie.

Specyfikacja Altera Cyclone IV FPGA

| Pozycja | Elementy logiczne | Moduł przetwarzania sygnału cyfrowego | Maksymalna wbudowana pamięć | Maksymalna liczba wejść/wyjść użytkownika | Opcja pakietu |

| EP4CE6 | 6000 | 15 | 270Kb | 179 | E144, U256, F256 |

| EP4CE10 | 10000 | 23 | 414 Kb | 179 | E144, U256, F256 |

| EP4CE15 | 15000 | 56 | 504Kb | 343 | E144, M164, U256, M256, F256, F484 |

| EP4CE22 | 22000 | 66 | 594 Kb | 153 | E144, U256, F256 |

| EP4CE30 | 29000 | 66 | 594 Kb | 532 | U484, F324, F484, F780 |

| EP4CE40 | 40000 | 116 | 1.134 Mb | 532 | U484, F324, F484, F780 |

| EP4CE55 | 56000 | 154 | 2.34 Mb | 374 | U484, F484, F780 |

| EP4CE75 | 75000 | 200 | 2.745 Mb | 426 | U484, F484, F780 |

| EP4CE115 | 114000 | 266 | 3.888 Mb | 528 | F484, F780 |

| EP4CGX15 | 14000 | 0 | 540 Kb | 72 | F169 |

| EP4CGX22 | 21000 | 40 | 756 Kb | 150 | F169, F324 |

| EP4CGX30 | 29000 | 80 | 1.08 Mb | 290 | F169, F324, F484 |

| EP4CGX50 | 50000 | 140 | 2.502 Mb | 310 | F484, F672 |

| EP4CGX75 | 74000 | 198 | 4.158 Mb | 310 | F484, F672 |

| EP4CGX110 | 109000 | 280 | 5.49 Mb | 475 | F484, F672, F896 |

| EP4CGX150 | 150000 | 360 | 6.48 Mb | 475 | F484, F672, F896 |

Cechy Altera Cyclone IV FPGA

Dostępne dwie podserie

Altera Cyclone IV FPGA jest dostępny w dwóch podseriach. Jednym z nich jest seria E, drugi to GX FPGA. Seria E charakteryzuje się typowym zużyciem energii statycznej, Gama GX oferuje użytkownikom niższą cenę i projekt integracji. Ma na celu maksymalne zaspokojenie zróżnicowanego popytu na rynku.

Mniejszy koszt PCB

Wszystkie typy układów w rodzinie Cyclone IV FPGA wymagają tylko dwóch baterii, prowadzące do uproszczenia sieci dystrybucyjnej, tania płytka drukowana, oszczędzająca miejsce płytka drukowana i krótki czas projektowania. Zintegrowany transceiver na platformie FPGA w znacznym stopniu przyczynia się do integracji projektu płyty głównej. Oprócz, elastyczne ramy zegara transiwera są kompatybilne z różnymi protokołami, gdy w pełni wykorzystuje wszystkie dostępne zasoby.

Dodatkowo, chip z serii Cyclone IV GX dobrze radzi sobie z oszczędnością miejsca, dzięki czemu można go zastosować na małych płytkach drukowanych przy niższych kosztach.

Zoptymalizowane ramy

Dzięki pionierskiej technice przetwarzania zastosowanej w urządzeniu przenośnym, Cyklon IV zmniejsza upływ prądu i zmniejsza moc statyczną. co więcej, wykorzystuje wiele technik i struktur wzmacniających, w tym materiał o niskiej stałej dielektrycznej, zmienna długość kanału i grubość tlenku, i napięcie progowe wielu tranzystorów.

Zintegrowany nadajnik-odbiornik

Cyclone IV GX FPGA jest wyposażony w doskonałą technikę transceivera, który słynie z wydajności jitter i doskonałej integralności sygnału. Co więcej, wyróżnia się kompatybilnością z różnymi protokołami szeregowymi. Nie mniej ważny, ma zastosowanie do PCI Express x1, x2 i x4 w konfiguracji portu głównego i punktu końcowego z własnością intelektualną (IP) Moduły podstawowe.

Jak mogę zdobyć płytki rozwojowe FPGA Altera Cyclone IV?

Zamów chipy od Intel lub Xilinx

Otrzymasz zestaw ze wszystkimi komponentami do wykonania płytki FPGA firmy Intel lub Xilinx. jednak, kondensatory do odsprzęgania, rezystor do punktów pomiarowych oraz rezystory małej mocy należy przygotować we własnym zakresie. Z gotowością elementów PCB i projektem, możesz opracować idealne płytki rozwojowe Altera Cyclone IV FPGA.

Zamów gołą płytę z chipami Cyclone IV i samodzielnym montażem

Otrzymasz płytkę z blokami logicznymi i transceiverem, ale bez projektów. Projektanci mogą bardzo wygodnie dodawać opcjonalne komponenty i budować kompletną platformę do testowania funkcji płytki.

Zamów płytki FPGA z chipami Cyclone IV w firmie Board Assembly House

Otrzymasz kompletny projekt płytki FPGA, osadzony projekt, wymagane komponenty i zmontowana płytka Cyclone IV FPGA z domu montażu płytek.

Typowe problemy podczas pracy dla płytek rozwojowych FPGA Altera Cyclone IV

Normalny prąd powinien przechodzić przez PLL VCCA

Dolna podkładka EP4CE6E22 zapakowana poprzez T144 została połączona z masą. Po podłączeniu do akumulatora, płyta działa normalnie. jednak, po podłączeniu do FPGA i konfiguracji, wyniki automatycznego wykrywania przez QUARTUS wskazują na niemożność skanowania łańcucha urządzeń. W międzyczasie, Debugger JTAG sugeruje nieprawidłowy zawór zegarowy. Wygląda na to, że chipy są odłączone. Nie mniej ważny, multimetr pokazuje, że nie ma zwarcia pomiędzy czterema rezystorami uziemiającymi dla JTAG.

ZA: Przed PLL VCCA dodano filtr dolnoprzepustowy z nadmiernym rezystorem. Wynik ten dotyczy tylko 0.6 napięcie między końcami PLL VCCA. jednak, według podręcznika, powinniśmy pozwolić na normalny prąd przez VCCA PLL bez względu na to, czy używamy tego VCCA, czy nie. A zatem, właściwym rozwiązaniem jest zmniejszenie rezystora filtra do 0 Om.

Podkładka łącząca obwodu pobierania powinna być podłączona do uziemienia

Jedna ręka, JTAG został pobrany i program działa normalnie, ale coś jest nie tak z pobieraniem pliku JIC JTGA. Z drugiej strony, ASP został poprawnie pobrany, ale program nie może się załadować, gdy zasilanie jest włączone.

Rezystory podciągające i rezystory podciągające oraz ich lutowanie jest OK. Czwarty 13.1 i programowanie jest dobre. Nie ma problemu z chipem i lutowaniem chipów. Zasilanie chipa również działa dobrze. Oscylator jest w dobrym stanie, także.

ZA: Musi występować jakiś problem w obwodzie pobierania. Prawdopodobnie, Powodem, dla którego JTAG może działać dobrze, ale urządzenie nie może programować, jest to, że trzy sygnały w obwodzie pobierania są nieprawidłowe. Podręcznik EP4C mówi, że jeden z sygnałów powinien być podłączony do masy za pomocą rezystora. Więc, zapoznaj się z odpowiednim rozdziałem w instrukcji i zmień montaż.

Interfejs JTAG powinien działać dobrze podczas debugowania JTAG

Podczas debugowania płytek rozwojowych Altera Cyclone IV FPGA, pokazuje następujące błędy.

!Błąd: Wykryto problem z łańcuchem JTAG

!Błąd: Połączenie TDI z pierwszym wykrytym urządzeniem EP3C(10|5)/EP4CE(10|6) może być zwarte do GND

!Błąd: Połączenia TCK i TMS z urządzeniem przed pierwszym wykrytym urządzeniem EP3C(10|5)/EP4CE(10|6) może mieć problem

!Informacje: Wykryto 1 urządzenie(s)

!Informacje: Urządzenie 1: EP3C(10|5)/EP4CE(10|6)

ZA: Radzimy wykryć problem JTAG Programowanie układów scalonych interfejs. Lutowanie może zostać rozłączone lub zwarte.

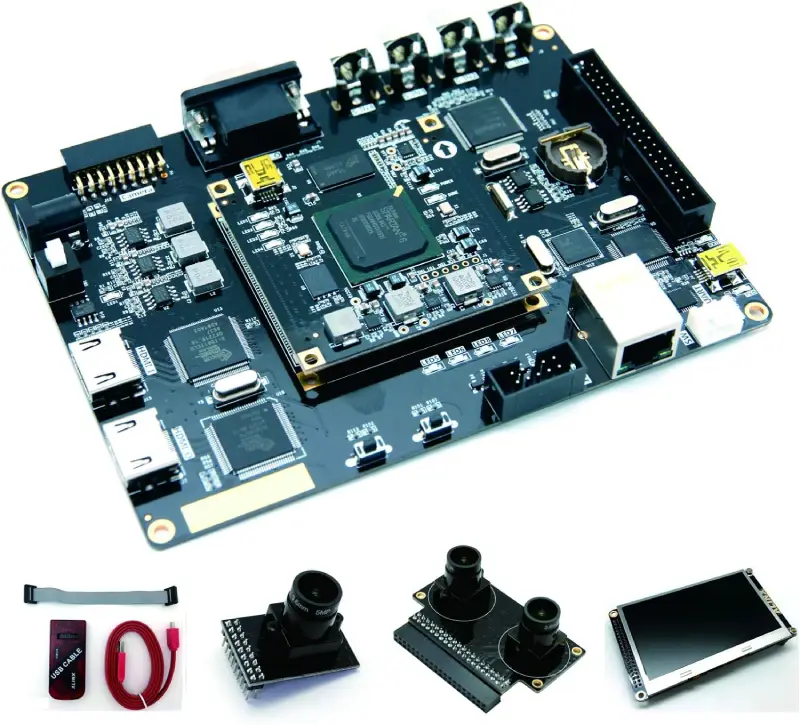

Top 3 Płytki rozwojowe Altera Cyclone IV FPGA

1. Płytki rozwojowe dla obrazu wideo IV

- FPGA: ALTERA Cyklon IV EP4CE75F23C8, 64*32bitowa pamięć DDR2,126M 9K RAM

- Wejście HDMI/Wyjście HDMI/Wyjście VGA/Gigabit Ethernet/Interfejs kamery CMOS/Interfejs debugowania ARM SWD/Interfejs debugowania FPGA JTAG

- Podaj schemat w formacie PDF, instrukcja obsługi i przykłady VHDL

2. Płytki rozwojowe dla kart graficznych Bluetooth

3. Tablice rozwojowe ds Pobierz USB Blaster i Sterowanie na podczerwień

Na wynos

Altera Cyclone IV FPGA to rodzina chipów przydatna w branży producentów elektroniki. Jeśli chcesz płytę rozwojową z tym chipem, nie krępuj się Skontaktuj się z nami.