電磁妨害 (EMI) 電磁干渉の一種です, エネルギーが放射線/伝導を通じてある電子デバイスから別の電子デバイスに伝達される, 信号品質を破壊します, 故障の原因となる. それは私たちの生活のほぼ隅々に存在します. 例えば, 携帯電話がラジオの近くにあるとき, ブーンという音が聞こえます, それが電磁干渉です. この問題は常に PCB 設計者を悩ませてきました。, 設計した電子製品が準拠していることを確認しなければならない人 EMC(電磁適合性). 実際には, 電磁干渉を完全に避けることは困難です, しかし、設計プロセス中にEMIを可能な限り低減することはできます。. 記事上で, PCB の電磁干渉を軽減するためのいくつかの重要な設計ルールをリストします。. すぐに飛び込みましょう.

PCB における電磁干渉の原因?

さまざまな要因があります, PCB 内での電磁干渉の発生に寄与するもの:

- 状態遷移の頻度が高いため、, マイクロプロセッサやメモリデバイスを含む高周波デジタル回路が一般的な原因である可能性があります.

- スイッチング電源と高速スイッチング トランジスタは、電流が急激に変化するため、EMI 放射の主な原因となります。.

- 信号トレースの設計または配線が不適切な場合、特に高周波信号を伝送する場合, アンテナとして機能するため、EMI の発生源になります。.

- グラウンドレベルのループや接地不良も、干渉電流による EMI の発生源となります。. 電源プレーンがシームレスに結合されていない場合, インピーダンスの不連続性が生じます, さらに信号反射やEMIを引き起こす.

- これらの問題は、コンポーネントの不適切な配置や不適切なシールドによって悪化する可能性があります。, これが、EMI が PCB 設計の主要な課題の 1 つである理由です。.

EMIを低減することがなぜ重要なのか?

まず第一に, FCC 規制の使用や、電子機器が販売される市場で義務付けられている CE マーキングなどの規制措置に準拠しています。. ガイドラインに従わない場合、再設計などの費用が増加する可能性があります, 製品の市場投入が遅れる, そしておそらく法的な問題もある.

第二に, EMIの低減により、使用される電子機器の性能と品質が向上します。. 高レベルの EMI は信号品質に望ましくないレベルに影響を与える可能性があります, データ破損の原因となる, システム障害またはデバイス全体の障害. 医療機器や自動車エレクトロニクスなどの繊細な用途, そのような問題は致命的になる可能性があります.

また, EMI を低減すると、各デバイスの動作が、携帯電話が無線に干渉するなど、近くにある他のデバイスの影響を受けなくなるため、ユーザー エクスペリエンスが向上します。.

最後に, 優れた EMI 設計は、電力効率と熱放散の向上にもつながります。, ポータブル製品のバッテリー寿命が長いと言い換えられる, 製品寿命の延長.

電磁干渉低減の主要な設計原則

PCB に関する一般的な EMC 問題は、基本的にトレースからの干渉に起因する設計の失敗に関連しています。, 回路, 方法, およびボード上のその他の関連機能. このセクションでは、電磁干渉の問題を軽減するための基本的な PCB 設計原則といくつかの異なる側面からのベスト プラクティスを紹介します。:

-

グランドプレーン

- 接地面積を最大化する:広い敷地面積に, 信号をより簡単に分散させてクロストークやノイズを低減できます。. したがって, PCB内のグランド領域を可能な限り増やす必要があります. 下地層が小さすぎる場合, 多層PCBを作成できます.

- 分割グランドプレーンは慎重に使用してください: 切断面の位置が適切でない場合は、分割は選択的に行う必要があります。, スロットアンテナの入手も可能です, EMI放射を強化します.

- 別々のグランドプレーン間の接続を最小限に抑える: 理想的には, 分割されたグランドプレーンを 1 か所だけでリンクする. 接地接続のいくつかのポイントは、ループを引き起こすという点で問題となる可能性があります。, これは、PCB からの排出量が増えることを意味します.

- バイパスコンデンサ配置の最適化: リターン電流経路とループ サイズを最小限に抑えた適切な方法で、バイパス コンデンサまたはデカップリング コンデンサをグランド プレーンにはんだ付けします。, EMIを低減するため.

-

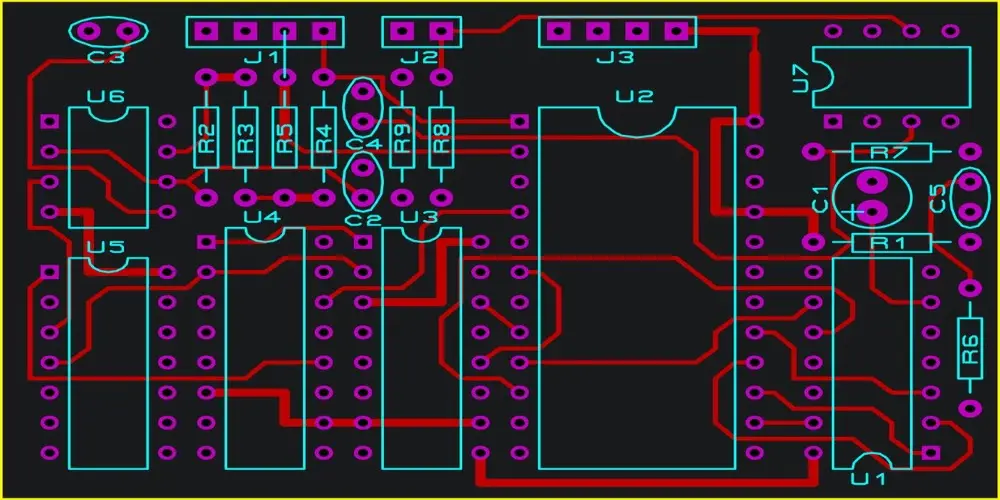

トレース レイアウト

- ベンドデザイン: 鋭い 90 度の曲がりを丸みのある角度または 45 度の角度に置き換えます. これにより、一貫したインピーダンスが維持され、信号の反射が軽減されます。.

- 信号の分離: 高速信号をフィルタリングすることが望ましい場合があります (たとえばクロックラインなど) 低速のものから. 干渉のレベルを減らすために、アナログ信号とデジタル信号を分離することをお勧めします。.

- リターンパスの最適化: デザインショート, 直接リターンパスを使用してループ領域を最小限に抑え、EMI を最小限に抑えます。.

- 差動ペアの配線: 差動トラックを近くに配線して結合を改善し、ノイズをコモンモードに移動させることで、差動入力の問題が軽減されます。.

- 使用方法による: を設計するとき、 PCB 方法, ビアは信号振幅の増加を引き起こし、追加のインダクタンスとキャパシタンスをもたらすため、賢明に行う必要があります。. 差動ペアの場合, ビアの使用をできる限り最小限に抑えるように努めなければなりません. 必要な場合にのみ、寄生容量を減らすために共通の楕円形アンチパッドを使用してください。.

-

コンポーネントの配置

- アナログとデジタルを分離する:同じ設計にアナログ回路とデジタル回路の両方がある場合, アナログ回路をデジタル回路からシールドし、独立したグランドを持つできるだけ多くの層を使用します。.

- アナログを高速から保護:アナログ回路をグランド信号でシールドして、何らかの保護を適用します。. 多層PCBの場合, アナログトレースと高速信号の間にグランドプレーンを配置します。.

- 高速コンポーネントの管理: 迅速な削減と分離, より多くのEMIを発生させる小さな部品. 高速信号の結合を最小限に抑え、信号が短く、グランドプレーンの近くに配置されるようにします。.

-

EMIシールド

EMIを完全に除去できない場合, どちらかを選択しなければなりません PCB シールド. ファラデーケージなどの外部シールドを利用して、回路基板全体をEMI源から遠ざけます。, 内部シールドはボード内の特定の敏感なコンポーネントを隔離します. ケーブルのシールド, 導電性コーティングまたは編組カバーを使用する, 高周波信号を封じ込め、EMI伝送を低減します。.

最終的な考え

結論として, 電磁干渉の低減は、PCB 設計の重要な側面であり、見逃すことはできません。. EMIの原因と応用設計手法を理解した上で, エンジニアは、EMI リスクから安全に動作できる高機能回路を PCB 上に作成できます。. 現代の電子機器はますます洗練され、私たちの生活の隅々にまで浸透しています。, これは、EMI の問題が今後もますます深刻になり続けることを意味します。. EMI低減の問題は複雑になる可能性がありますが、, 信頼できる PCB 設計専門家と協力することで、状況をより良い方向に変えることができます. 写真にMOKOが入っている場所です. 高性能PCB設計のノウハウを活用, 私たちは、EMI 削減に関連する問題への取り組みと電磁両立性の達成を支援する準備ができています。. MOKOテクノロジーにお問い合わせください 今すぐ!